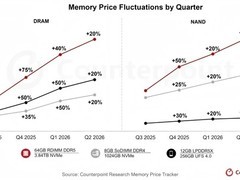

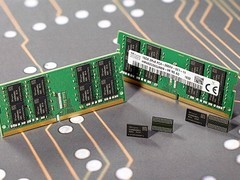

随着生成式人工智能、高性能计算以及数据中心对内存速度和能效要求的不断提升,新一代内存技术DDR6正逐步走向量产与普及。业内预计,DDR6将在2027年实现大规模商用。

目前,全球三大主要DRAM制造商均已启动DDR6相关研发工作,全面布局芯片设计、内存控制器及封装模组等关键技术环节,致力于推动产品落地。

根据国际标准组织JEDEC的规划进度,DDR6主规格的草案已于2024年底完成,而低功耗版本LPDDR6的规范草案也计划于2025年第二季度发布。后续预计在2026年进入平台级测试与验证阶段,为正式商用铺路。

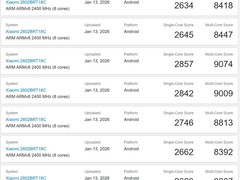

技术层面,DDR6在性能和架构上均有显著提升。初始传输速率可达8800MT/s,在产品生命周期内有望提升至17600MT/s,超频版本甚至可能突破21000MT/s,整体性能相较DDR5提升约两到三倍。

架构设计上,DDR6采用4×24-bit的通道结构,取代DDR5的2×32-bit方案,在数据并行处理能力、传输效率和频率利用方面更具优势。但该设计也对内存模组的I/O接口提出更高要求,增加了技术实现的复杂性。

与此同时,由JEDEC制定的CAMM2标准正逐渐成为DDR6时代的重要接口方案。其凭借高带宽、高集成度、低信号干扰和紧凑薄型的设计特点,有效克服了DDR5时代288针DIMM插槽在扩展性与电气性能上的瓶颈,为未来内存系统提供了更优的整合路径。

评论

更多评论