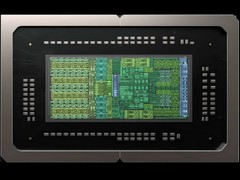

在2026年国际消费电子展期间,AMD展示了其最新一代Zen6架构的EPYC Venice处理器,该处理器成为全球首款基于台积电2纳米工艺打造的服务器级芯片。近期网络上出现了更多关于该处理器尚未公开的技术细节,进一步揭示了其架构设计方向。

EPYC Venice在核心规模上实现了显著突破,特别是搭载Zen 6C架构的版本,最高可实现256核配置。这一提升得益于更高密度的核心复合体设计以及全新的双IO Die结构。其中,Zen 6C核心复合体(CCD)成为关键组成部分,每颗CCD可集成32个核心,相较前代Zen 5C架构的16核容量实现翻倍。因此,仅需8颗CCD即可达成256核的顶级规格。

缓存系统同样得到增强,每颗Zen 6C CCD配备128MB L3缓存,整颗处理器累计可提供高达1GB的L3缓存总量,有助于提升数据密集型工作负载的处理效率。

在制程选择方面,Venice处理器采用差异化策略:负责计算任务的CCD模块使用台积电2纳米N2P工艺,以实现更高的能效与频率表现;而承担I/O功能的IO Die则继续采用6纳米工艺,兼顾成本与成熟度。

另一项重要变革在于引入双IO Die架构。两颗IO Die的总封装面积达到750平方毫米,远大于此前单颗IO Die的设计。这一结构有效扩展了内存通道数量,并显著增强了PCIe和CXL接口的连接能力,为AI训练服务器中多GPU协同及高速网络互连提供了更强的硬件支持。

评论

更多评论