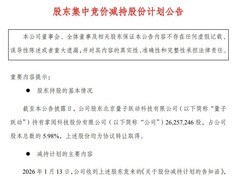

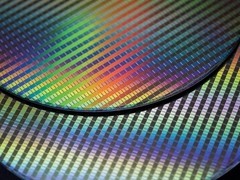

1月17日,据韩国媒体报道,三星电子第六代10纳米级DRAM内存制程工艺(即1c nm)的良率已提升至约60%,成功突破量产盈亏平衡点。这一进展被视为关键里程碑,因三星即将推出的HBM4内存正是基于该制程技术。更高的DRAM晶粒良率将有助于在HBM4产品上实现更优的成本控制与利润空间,从而增强整体业绩表现。

报道指出,三星电子在1c nm DRAM项目上已调整此前以良率优先、谨慎推进量产的策略,转而回归快速量产的传统模式,以更积极的姿态应对市场需求变化。此举有望帮助其从英伟达等主要客户处获得更多订单,强化市场竞争力。

此前有行业分析认为,在HBM3E平台需求持续强劲以及产品规格不断提升的背景下,高带宽内存产品的规模化生产预计最早将在2026年第一季度末逐步展开。目前,三星电子、SK海力士与美光仍有一定时间进一步优化产品良率,为下一阶段的市场竞争做好准备。

评论

更多评论