2025年12月21日,AMD近日正式发布了首份关于Zen6架构设计的技术文档AMD Family 1Ah Model 50h-57h处理器性能监控计数器,通过性能监控接口披露了Zen6架构的诸多关键细节。

此次披露的内容聚焦于EPYC数据中心处理器所采用的Zen6架构,虽未涉及消费级产品,但其底层设计思路具有广泛参考价值。

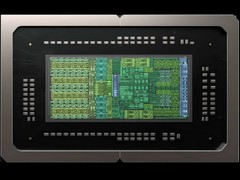

此前业界已知,EPYC Zen6将是首款采用台积电2nm制程工艺的高性能处理器,单颗芯片最高支持256个核心。而最新公布的文档显示,Zen6并非在Zen4或Zen5基础上进行小幅优化的迭代版本,而是一次全面重构的架构升级,专为高吞吐量计算场景打造,具备更宽的执行宽度。其指令调度引擎达到8路并行宽度,接近苹果同类设计的9路水平,同时继续保留对SMT同步多线程技术的支持。

Zen6在架构层面显著强化了对矢量运算与浮点运算状态的监测能力,反映出其对高强度数学计算负载的高度重视。每个核心均集成专用性能计数器,可精确追踪调度窗口空闲情况、后端流水线阻塞以及线程选择带来的性能损耗,进一步验证了该架构在宽发射机制与SMT资源调度策略上的深度优化。

在指令集支持方面,Zen6延续了对512位完整宽度AVX-512指令集的支持,兼容FP64、FP32、FP16及BF16等多种数据格式,并支持FMA融合乘加、MAC乘积累加等关键运算模式。同时支持浮点与整数混合的矢量运算,涵盖VNNI矢量神经网络指令、AES加密指令以及SHA安全哈希算法等功能。

尤为值得注意的是,Zen6在AVX-512指令的持续吞吐能力上实现显著提升,其每周期可完成的矢量运算量已超出传统性能测量手段的覆盖范围,因此必须依赖新型合并式性能计数器才能实现准确监控。近年来,AVX-512已成为AMD在高性能计算领域的重要技术优势,而Zen6的表现进一步巩固了这一地位。

综合来看,Zen6标志着AMD首次从底层出发,专门针对数据中心与人工智能应用需求构建的全新微架构,将在高性能计算领域展现强大潜力。至于未来消费级产品将继承哪些特性,实际运行表现如何,仍有待后续信息揭晓。

评论

更多评论