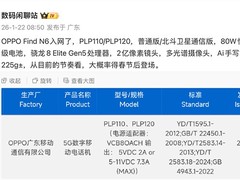

JEDEC组织正加速推进一项名为SPHBM4(标准封装高带宽内存第四代)的新内存标准制定工作。该技术仅需512-bit位宽即可实现与HBM4相当的完整带宽水平,同时支持传统有机基板,在确保高性能的同时有效降低集成成本,并提升单封装容量上限。

这一新型内存架构定位介于传统DDR与当前主流HBM之间,旨在覆盖HBM未能深入拓展的多个应用领域。尽管具备高带宽特性,但其设计初衷并非用于替代显卡中的GDDR显存,也不会进入消费级图形市场。

现有HBM内存普遍采用1024-bit或2048-bit超高位宽设计,虽带来卓越的带宽表现和能效优势,但也因占用过多芯片面积而限制了堆叠层数与总容量,进而影响AI加速器及大型计算集群的整体性能扩展能力。SPHBM4通过引入4:1串行传输机制,将物理位宽从2048-bit压缩至512-bit,同时维持等效带宽输出,性能仍显著优于DDR5内存。

目前JEDEC尚未明确说明其实现方式是通过将数据传输速率提升至32GT/s——即原有速率的四倍,还是采用了更高频率下的新型编码技术来达成目标带宽。无论具体路径如何,SPHBM4在封装内部沿用了行业通用的基础Die以及HBM4标准Die,确保单堆叠容量可与HBM4及HBM4E保持一致,最高可达64GB。此举也有助于简化控制器架构和整体封装结构,进一步优化制造成本。

理论上,得益于结构改进和集成效率提升,SPHBM4的潜在容量上限可达到HBM4的四倍,展现出更强的扩展潜力。

回顾过往,HBM曾作为高端显卡显存出现,但SPHBM4并不会重走这条路线。其核心设计目标聚焦于实现HBM4级别的带宽水平,优先保障性能与容量需求,而非追求极致的成本控制或功耗优化。虽然相比HBM4和HBM4E,SPHBM4可通过省去昂贵的中介层实现一定程度的成本下降,但由于仍采用堆叠结构,并依赖配套的基片接口、TSV硅通孔以及先进封装工艺,整体成本远高于常规DRAM方案。

因此,在显卡产品中使用单颗SPHBM4替代多颗GDDR6或GDDR7的方案并不可行:不仅会导致成本上升,且性能增益有限,难以形成实际优势。

评论

更多评论