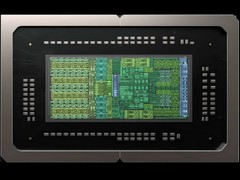

存储领域的三大主要企业正积极推进16层堆叠HBM内存芯片的研发,计划于2026年第四季度启动向主要客户供货。这一进展旨在满足高性能计算特别是人工智能加速器对更高带宽和更大容量的需求。

据产业链消息,相关客户已明确提出在2026年第四季度接收16-Hi HBM产品的时间节点,以支持其高端AI计算平台的部署。业内人士透露,继完成12层堆叠HBM4产品后,市场需求迅速转向更高密度的16层方案,因此各厂商正在制定紧凑的研发路线图,初步性能测试有望在2025年第三季度前后展开。

目前,16层堆叠HBM尚未进入量产阶段,技术挑战显著。随着堆叠层数上升,DRAM芯片的三维集成复杂度急剧增加。按照JEDEC规范,HBM4模块总厚度上限为775微米,在此空间内容纳16层DRAM,要求单颗晶圆厚度由当前约50微米降至30微米左右。如此薄的晶圆在制造、搬运和封装过程中极易发生破裂或变形,对工艺稳定性提出极高要求。

此外,芯片间的粘合材料与工艺成为关键技术竞争点。不同厂商采用的技术路径有所差异:部分企业倾向使用TC-NCF方案,另一些则坚持采用MR-MUF工艺。为实现更高层数堆叠,粘合层厚度需压缩至10微米以下,同时必须保障足够的热导率以应对高密度集成带来的散热难题,这对材料科学与封装技术构成双重考验。

业界普遍认为,16层堆叠将成为未来多年HBM发展的关键节点。根据现有技术演进规划,下一代HBM5仍将维持最多16层堆叠,直至2035年前后的HBM7才有望实现20至24层堆叠,而后续的HBM8亦预计以24层为上限。这意味着16-Hi不仅是一项性能升级,更将长期影响整个高带宽内存架构的发展方向。

评论

更多评论