2026年1月16日,随着3D V-Cache技术通过堆叠L3缓存持续在游戏处理器领域占据优势,AMD继续推进其缓存架构的演进。近期,该公司公开一项名为均衡延迟堆叠缓存的技术研究,专利编号为US20260003794A1,展示了其在下一代缓存设计中的新方向——将堆叠结构应用于L2缓存。

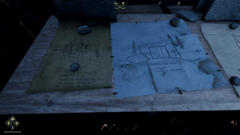

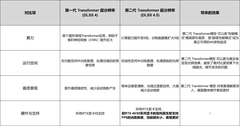

目前广泛应用的3D V-Cache技术主要通过在计算核心的上下方叠加额外的L3缓存来增强数据访问效率与容量,而这项新提案则表明,AMD正着手将堆叠理念延伸至更靠近核心、速度更快的L2层级。根据提供的结构示意图,该方案采用多层堆叠设计,底层负责连接处理器核心与缓存模块,其上可集成多个缓存芯片层。例如,一个由四组512KB区域构成的2MB L2缓存模块,未来还可扩展至4MB容量。

该堆叠机制沿用了与现有3D V-Cache相似的技术路径,借助硅通孔(TSV)实现L2与L3缓存层之间的垂直互联,并将其整合于基础芯片及计算复合体之上,整体布局围绕中心垂直轴进行数据调度,由CCC单元统一管理输入输出流程。

研究文献中以1MB和2MB的平面L2缓存作为对照基准指出,传统平面结构下的1MB L2缓存平均延迟约为14个时钟周期,而采用堆叠方式实现的同容量缓存可将延迟降低至12个周期。这意味着,堆叠型L2缓存不仅能够显著提升存储容量,还能在响应速度上达到甚至优于传统设计的水平。同时,AMD强调,这种新型架构在能效方面也展现出明显优势,有助于降低整体功耗。

评论

更多评论