1月16日,美国商标和专利局公布了一份由AMD提交的技术专利,名为均衡延迟堆叠缓存,标志着该公司在处理器缓存架构上的进一步探索。该专利提出将3D堆叠技术从现有的三级缓存(L3)延伸至二级缓存(L2),旨在优化数据访问效率并提升整体能效表现。

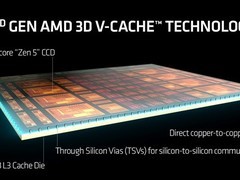

L2缓存可被理解为CPU内部的数据中转枢纽,其速度远超主内存,虽略慢于一级缓存(L1),但在处理器核心调用数据的过程中承担关键角色。其容量与响应速度直接影响计算任务的执行流畅度。当前采用3D V-Cache技术的Ryzen X3D系列处理器仅在L3缓存层面应用堆叠设计,而此次新专利则聚焦于L2层级的垂直扩展,试图通过结构创新进一步压缩延迟。

根据专利文件描述,AMD计划采用硅通孔(TSV)或键合焊盘过孔(BPV)等先进连接工艺,在多层堆叠芯片之间构建垂直通信路径。与传统布局不同,该项设计将连接过孔集中布置于芯片堆叠结构的几何中心位置。这种对称性布局有助于缩短信号传输距离,减少布线层级,并使各缓存层之间的访问时长趋于一致,从而降低因路径差异带来的延迟波动和能量损耗。

专利中提供的技术参数显示,该方案具备显著的性能潜力。以容量为1MB的标准L2缓存为例,采用新型堆叠结构后,数据访问所需时钟周期可由常规设计的14个缩减至12个。尽管数值变化看似微小,但在现代CPU微架构中,L2访问周期普遍处于10至50个时钟周期范围内,因此两周期的优化已属实质性进步,有望带来可观的运算效率提升。

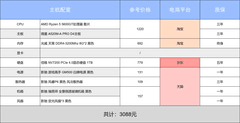

回顾发展历程,AMD自2021年起便率先推出基于L3缓存堆叠的3D V-Cache技术,并已完成技术迭代,第二代方案已在最新发布的高性能桌面处理器中投入使用。近期亮相的一款搭载该技术的八核产品,更因其在游戏场景中的卓越表现引发关注。

目前该项涉及L2堆叠缓存的新专利仍处于公示阶段,编号为US20260003794A1。尽管其理论优势明确,但专利转化为实际产品通常需经历较长的研发与验证周期,最终落地效果还将受到制造工艺、散热管理及电路设计等多种物理因素制约。

评论

更多评论